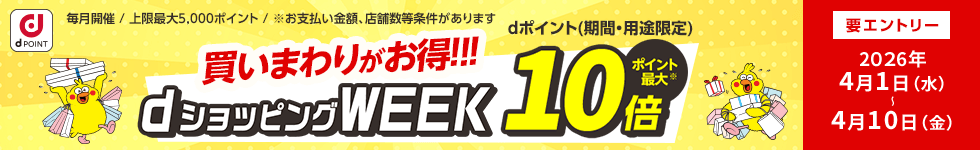

4/7

時点_ポイント最大10倍

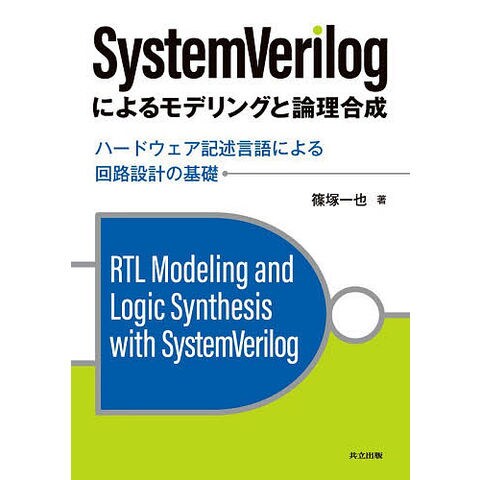

SystemVerilogによるモデリングと論理合成 ハードウェア記述言語による回路設計の基礎/篠塚一也

販売価格

5,060

円 (税込)

送料無料

- 出荷目安:

- 1~3日で発送予定

たまるdポイント(通常) 46

+キャンペーンポイント(期間・用途限定) 最大9倍

※たまるdポイントはポイント支払を除く商品代金(税抜)の1%です。

※表示倍率は各キャンペーンの適用条件を全て満たした場合の最大倍率です。

各キャンペーンの適用状況によっては、ポイントの進呈数・付与倍率が最大倍率より少なくなる場合がございます。

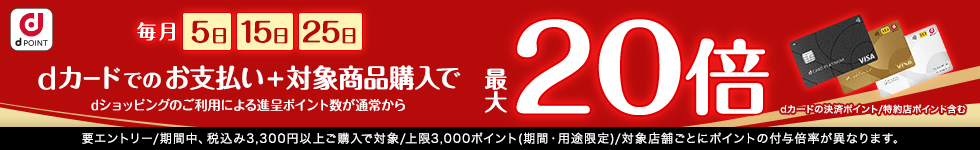

dカードでお支払ならポイント3倍

各キャンペーンの適用状況によっては、ポイントの進呈数・付与倍率が最大倍率より少なくなる場合がございます。

- 商品情報

- レビュー

篠塚一也

共立出版

ISBN:4320125924/9784320125926

発売日:2026年01月

※商品画像はイメージや仮デザインが含まれている場合があります。帯の有無など実際と異なる場合があります。

【内容紹介】

今日では、ハードウェア記述言語はハードウェア設計・検証に欠かせない手段となっています。本書は、ハードウェア記述言語としてSystemVerilogを採用し回路設計をするために必要な基礎知識と基礎技術を解説しています。

基礎知識には、論理回路をハードウェア記述言語で表現する知識およびハードウェア記述言語で表現された記述を論理回路に合成する知識が含まれます。また、基礎技術には、記述表現から合成された回路構成を最適化する手法が含まれます。これらの基礎知識と技術を養う事によりハードウェア記述言語による回路設計を効果的に行えるようになります。

その他、従来では思いもよらなかった斬新な記述法も紹介しています。例えば、変数aがlogic 「7 0」と宣言されているとすると、 a )) 1 という演算の代わりにa「7 1」を指定できます。あるいは、2のN乗(Nは定数)の操作は 1 (( N と書かれますが、この記法では定数1の精度に依存するためNはその精度以上にはなりえません。しかし、SystemVerilogでは{1'b1、N{1'b0}}とも書けます。この記法ではシフト後も上位の桁を失いません。このように、SystemVerilogの基本的な機能を正確に理解し応用する事により従来では成し得なかった機能表現が可能になります。総じて、本書はSystemVerilogによる新時代の設計手法の基礎知識を提供します。

共立出版

ISBN:4320125924/9784320125926

発売日:2026年01月

※商品画像はイメージや仮デザインが含まれている場合があります。帯の有無など実際と異なる場合があります。

【内容紹介】

今日では、ハードウェア記述言語はハードウェア設計・検証に欠かせない手段となっています。本書は、ハードウェア記述言語としてSystemVerilogを採用し回路設計をするために必要な基礎知識と基礎技術を解説しています。

基礎知識には、論理回路をハードウェア記述言語で表現する知識およびハードウェア記述言語で表現された記述を論理回路に合成する知識が含まれます。また、基礎技術には、記述表現から合成された回路構成を最適化する手法が含まれます。これらの基礎知識と技術を養う事によりハードウェア記述言語による回路設計を効果的に行えるようになります。

その他、従来では思いもよらなかった斬新な記述法も紹介しています。例えば、変数aがlogic 「7 0」と宣言されているとすると、 a )) 1 という演算の代わりにa「7 1」を指定できます。あるいは、2のN乗(Nは定数)の操作は 1 (( N と書かれますが、この記法では定数1の精度に依存するためNはその精度以上にはなりえません。しかし、SystemVerilogでは{1'b1、N{1'b0}}とも書けます。この記法ではシフト後も上位の桁を失いません。このように、SystemVerilogの基本的な機能を正確に理解し応用する事により従来では成し得なかった機能表現が可能になります。総じて、本書はSystemVerilogによる新時代の設計手法の基礎知識を提供します。

※本データはこの商品が発売された時点の情報です。